## PHÝCHIPS

# PR7

## RAIN RFID Reader SoC

The PR7 is a true single SoC solution for RAIN RFID reader/writer which integrated high performance UHF RF/Analog, MODEM, ARM Cortex-M3 processor, Flash memory and many other features with fully compliant EPC Global Gen2v2/ISO18000-63 protocol. With high integration and excellent performance, it will be a new product that leads the market by being used in various fields ranging from handheld to fixed readers.

#### **Key Feature**

- RAIN RFID Reader SoC

- Frequency range: 860 ~ 930MHz

- 3.3V single power supply

- ARM Cortex-M3

- 256KB Embedded Flash

- 128KB SRAM

- PR-ASK, DSB-ASK

- Support DRM

- EPC Gen2v2

- 8mm x 8mm 96-pin LGA package

## Version History

| Version | Date       | Description                                                 |

|---------|------------|-------------------------------------------------------------|

| 0.1.0   | 2024.01.29 | First edition                                               |

| 0.1.1   | 2024.01.30 | Updated measurement data                                    |

| 0.1.2   | 2024.07.03 | Format revision                                             |

| 0.1.3   | 2024.10.10 | Modified the transition time for each operation mode in 5.1 |

|         |            | Modified power up timing and description in 6               |

|         |            |                                                             |

|         |            |                                                             |

|         |            |                                                             |

## Contents

| 1. | System   | Overview                             | 5  |

|----|----------|--------------------------------------|----|

|    | 1.1      | Instruction                          | 5  |

| 2. | Specific | cations                              | 6  |

|    | 2.1      | Absolute Maximum Ratings             | 6  |

|    | 2.2      | Operating conditions                 | 6  |

|    | 2.3      | Current consumption                  | 6  |

|    | 2.4      | Radio Receiver specification         | 6  |

|    | 2.5      | Radio Transmitter specifications     | 7  |

|    | 2.6      | Frequency Synthesizer specifications | 7  |

|    | 2.7      | Peripheral specifications            | 7  |

|    | 2.8      | Timing specifications                | 8  |

|    | 2.8.     | .1 I2C                               | 8  |

|    | 2.8.     | .2 SPI                               | 8  |

| 3. | Pin des  | cription                             | 9  |

| 4. | Functio  | nal Description                      | 12 |

|    | 4.1      | RF                                   | 12 |

|    | 4.1.     | .1 Receiver path                     | 12 |

|    | 4.1.     | .2 Transmitter path                  | 13 |

|    | 4.1.     | .3 Frequency synthesizer             | 13 |

|    | 4.1.     | .4 Others                            | 13 |

|    | 4.2      | MCU                                  | 14 |

|    | 4.2.     | .1 Feature                           | 14 |

|    | 4.2.     | .2 UART                              | 14 |

|    | 4.2.     | .3 I2C                               | 14 |

|     | 4.2.4     | SPI                                 | 15 |

|-----|-----------|-------------------------------------|----|

|     | 4.2.5     | QSPI (Quad-SPI)                     | 15 |

|     | 4.2.6     | USB                                 | 15 |

|     | 4.2.7     | Timer                               | 15 |

|     | 4.2.8     | Watchdog timer                      | 16 |

|     | 4.2.9     | DMA                                 | 16 |

|     | 4.2.10    | TRNG (True Random Number Generator) | 17 |

|     | 4.2.11    | Debug Mode                          | 17 |

|     | 4.2.12    | GPIO                                | 17 |

|     | 4.2.13    | Interrupt                           | 18 |

|     | 4.2.14    | Memory Organization                 | 19 |

|     | 4.2.15    | Port Map                            | 20 |

| Sys | tem Con   | ntrol                               | 21 |

| 5.1 | Ope       | eration mode                        | 21 |

|     | 5.1.1     | IDLE mode                           | 21 |

|     | 5.1.2     | ACTIVE mode                         | 21 |

|     | 5.1.3     | SLEEP mode                          | 21 |

|     | 5.1.4     | DEEPSLEEP mode                      | 21 |

|     | 5.1.5     | STOP mode                           | 22 |

| Pov | wer up ti | iming                               | 23 |

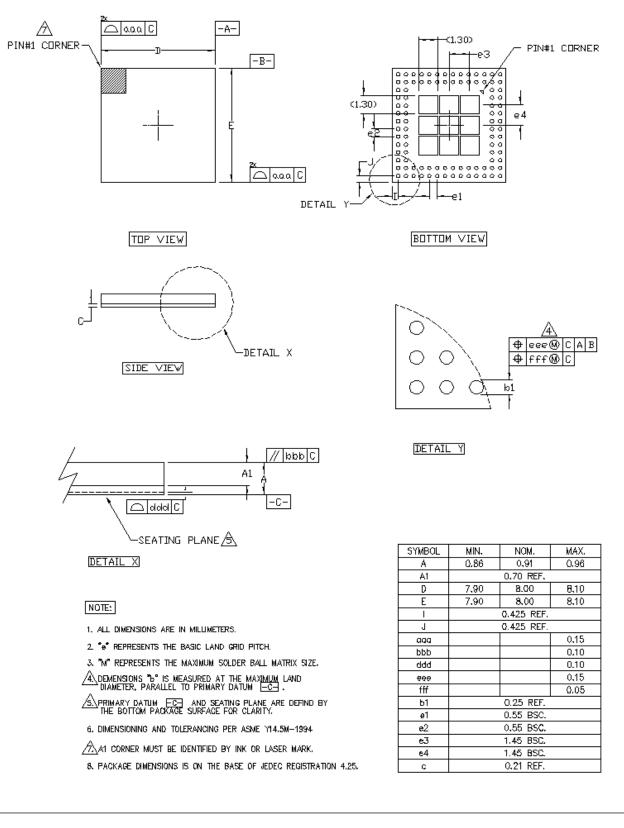

| Pac | kage Inf  | formation                           | 24 |

| 7.1 | Pack      | kage Dimensions                     | 24 |

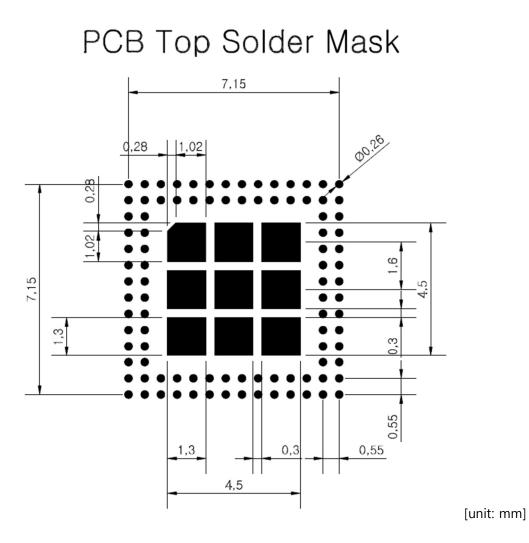

| 7.2 | PCB       | layout                              | 25 |

5.

6.

7.

## 1. System Overview

#### 1.1 Instruction

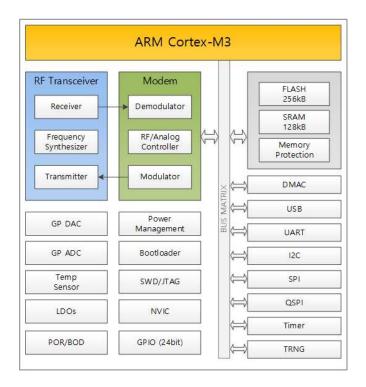

Figure 1 PR7 Overall block diagram

PR7 consolidates RF/Analog, MODEM, and MCU functionalities into a single chip. The RF transceiver employs a direct conversion structure, while the MODEM fully adheres to the EPC gen2v2 air protocol. Additionally, it provides support for various standards based on ISO 18000-6 (ISO18000-62, 18000-63, 18000-64). The chip includes a built-in Power-On Reset (POR) and Brown-Out Detector (BOD), along with an integrated Low Drop-Out (LDO) for core power generation. The MCU is built on the ARM Cortex-M3 architecture, featuring 256 kB of embedded flash and 128 kB of SRAM. It offers support for USB (12Mbps) and various serial interfaces, including UART, I2C, SPI, and QSPI.

The following documents provide additional information.

Firmware Development user manual Firmware download & debugging manual WINE Reader Control Protocol manual WINE API user manual PR7 reference design

## 2. Specifications

## 2.1 Absolute Maximum Ratings

| Parameter                            | Condition | Min. | Тур. | Max. | Unit |

|--------------------------------------|-----------|------|------|------|------|

| Supply voltage                       |           |      |      |      | V    |

| Storage Temperature                  |           | -55  |      | +125 | °C   |

| Electrostatic discharge rating (HBM) |           |      | 2000 |      | V    |

## 2.2 Operating conditions

| Parameter                     | Condition | Min. | Тур. | Max. | Unit |

|-------------------------------|-----------|------|------|------|------|

| Ambient operating temperature |           | -40  |      | +85  | °C   |

| Supply voltage                |           |      | 3.3  |      | V    |

## 2.3 Current consumption

| Parameter | Mode      | Condition                          | Min. | Тур. | Max. | Unit |

|-----------|-----------|------------------------------------|------|------|------|------|

|           | Active    | CW on, DA on, Tx PA off, LCA min   |      | 145  |      | mA   |

|           |           | CW on, DA on, Tx PA 20dBm, LCA min |      | 310  |      | mA   |

| PR7       | IDLE      | CW off, RF off                     |      | 35   |      | mA   |

| Chip only | SLEEP     | CPU sleep                          |      | 16   |      | mA   |

|           | DEEPSLEEP | -                                  |      | TBD  |      | uA   |

|           | STOP      | -                                  |      | TBD  |      | uA   |

1) Supply voltage:  $VCC_xx = 3.3V$

## 2.4 Radio Receiver specification

| Parameter               | Condition             | Min. | Тур. | Max. | Unit |

|-------------------------|-----------------------|------|------|------|------|

| Input Frequency         |                       | 860  |      | 930  | MHz  |

| Full path gain          | In-band gain          | 18   |      | 80   | dB   |

| Gain control range      |                       |      | 63   |      | dB   |

| Analog filter bandwidth | 3dB cut-off frequency | 60   |      | 1000 | kHz  |

## 2.5 Radio Transmitter specifications

| Parameter          | Condition  | Min. | Тур. | Max. | Unit |

|--------------------|------------|------|------|------|------|

| Tx DA output power | @ Max gain |      | 6    |      | dBm  |

| Tx PA output power |            |      | 21   |      | dBm  |

| Tx PA gain         | @ Max gain |      | 20   |      | dB   |

## 2.6 Frequency Synthesizer specifications

| Parameter                 | Condition | Min. | Тур. | Max. | Unit   |

|---------------------------|-----------|------|------|------|--------|

| Reference clock frequency |           |      | 32   |      | MHz    |

| Frequency Range           |           | 860  |      | 930  | MHz    |

| Lo phase noise            |           |      |      |      |        |

| @ 10kHz                   |           |      | -67  |      | dBc/Hz |

| @250kHz                   |           |      | -118 |      | dBc/Hz |

| @1MHz                     |           |      | -127 |      | dBc/Hz |

## 2.7 Peripheral specifications

TBD

## 2.8 Timing specifications

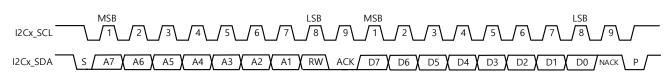

#### 2.8.1 I2C

| Parameter         | Condition | Min. | Тур. | Max. | Unit |

|-------------------|-----------|------|------|------|------|

| I2C_SCL frequency |           |      |      | 400  | kHz  |

#### 2.8.2 SPI

| SPIx_SCK<br>(CPOL=0)  |    |      |   |   |   |   |   |   |     |

|-----------------------|----|------|---|---|---|---|---|---|-----|

| SPIx_SCK<br>(CPOL=1)  |    |      |   |   |   |   |   |   |     |

| SPIx_MOSI<br>(CPHA=0) | MS | в    | X | X | X | X | X | X | LSB |

| SPIx_MOSI<br>(CPHA=1) |    | M\$B | X | X | X | X | X | X | LSB |

| Parameter                | Condition | Min. | Тур. | Max. | Unit |

|--------------------------|-----------|------|------|------|------|

| SPIx_SCK clock frequency | Master    |      |      | 64   | MHz  |

## 3. Pin description

|   | 1          | 2          | 3           | 4         | 5           | 6         | 7        | 8         | 9        | 10    | 11        | 12        | 13     | 14    |

|---|------------|------------|-------------|-----------|-------------|-----------|----------|-----------|----------|-------|-----------|-----------|--------|-------|

| А | RXM_QOUTP  | RXBB_QINP  | RXBB_IINP   | VDDA_BBA  | NC          | GPADC_IN  | XOUT_32K | VCC_IO3   | PORb     | DM    | VCCU      | VCCD2     | PA1    | PA2   |

| в | RXM_QOUTN  | VDDA_RFRX  | RXBB_QINN   | RXBB_IINN | NC          | VDDA_DIG  | XIN_32K  | WAKEUPb   | PORb_OUT | DP    | VDDD2     | PA0       | PA4    | PA3   |

| с | RXM_IOUTN  | RXM_IOUTP  |             |           |             |           |          |           |          |       |           |           | PA6    | PA5   |

| D | RX_IN      | VCC_IO1    |             |           |             |           |          |           |          |       |           |           | PB0    | PA7   |

| Е | VDDA_LCA   | LEAKOUT    |             |           | GND         |           |          | GND       |          |       | GND       |           | PB2    | PB1   |

| F | LEAKIN     | LCA_LDOOUT |             |           |             |           |          |           |          |       |           |           | PB4    | PB3   |

| G | LCA_VBIAS2 | LCA_VBIAS1 |             |           |             |           |          |           |          |       |           |           | PB6    | PB5   |

| н | VDDA_LOGEN | VCC_IO2    |             |           | GND         |           |          | GND       |          |       | GND       |           | PC0    | PB7   |

| J | CPOUTP     | VDDA_VCO   |             |           |             |           |          |           |          |       |           |           | PC[2]  | PC[1] |

| к | CPOUTN     | VDDA_CP    |             |           |             |           |          |           |          |       |           |           | RESETb | PC[3] |

| L | TXPA_OUTP  | VDDA_PLL   |             |           | GND         |           |          | GND       |          |       | GND       |           | PC[4]  | VCCF  |

| м | TXPA_OUTN  | TXPA_BIAS2 |             |           |             | · · · ·   |          |           |          |       |           |           | PC[6]  | PC[5] |

| N | VCC_PA2    | TXPA_V25   | TXPA_IN     | VDDA_RFTX | GPDACOUTP   | GPDACOUTN | NC       | VDD_TCXO  | NC       | VDDD1 | TDO/SWO   | TCK/SWCLK | NC     | PC[7] |

| Ρ | TXPA_BIAS1 | VCC_RFTX   | TXPA_LDOOUT | TXDA_OUT  | RFTX_LDOOUT | XIN_32M   | XOUT_32M | DIG_CPOUT | VCC_IO4  | VCCD1 | TMS/SWDIO | TDI       | nTRST  | NC    |

| No | Name       | IO | Туре   | Description                              |

|----|------------|----|--------|------------------------------------------|

| A1 | RXM_QOUTP  | 0  | Analog | Rx mixer Q path positive/negative output |

| B1 | RXM_QOUTN  |    |        |                                          |

| C1 | RXM_IOUTN  | 0  | Analog | Rx mixer I path positive/negative output |

| C2 | RXM_IOUTP  |    |        |                                          |

| A2 | RXBB_QINP  | Ι  | Analog | Rx BBA Q path positive/negative input    |

| B3 | RXBB_QINN  |    |        |                                          |

| A3 | RXBB_IINP  | Ι  | Analog | Rx BBA I path positive/negative input    |

| B4 | RXBB_IINN  |    |        |                                          |

| A4 | VDDA_BBA   | Р  | Analog | LDO output for BBA                       |

| D2 | VCC_IO1    | Р  | Analog | Power supply (IO1)                       |

| D1 | RX_IN      | I  | RF     | Rx RF input                              |

| B2 | VDDA_RFRX  | Р  | Analog | LDO output for RF RX                     |

| F1 | LEAKIN     | Ι  | RF     | LCA (Leakage Cancellation Amp) input     |

| E2 | LEAKOUT    | 0  | RF     | LCA (Leakage Cancellation Amp) output    |

| G2 | LCA_VBIAS1 | 0  | Analog | LCA voltage bias1: capacitor is required |

| G1 | LCA_VBIAS2 | 0  | Analog | LCA voltage bias2: capacitor is required |

| E1 | VDDA_LCA   | Р  | Analog | LCA DC power input                       |

| F2 | LCA_LDOOUT | 0  | Analog | LDO output for LCA: connect to VDDA_LCA  |

| No  | Name        | IO | Туре    | Description                                          |

|-----|-------------|----|---------|------------------------------------------------------|

| H1  | VDDA_LOGEN  | Р  | Analog  | LDO output for LO gen                                |

| H2  | VCC_IO2     | Р  | Analog  | Power supply (IO2)                                   |

| J1  | CPOUTP      | 0  | Analog  | RFPLL Charge Pump output                             |

| К1  | CPOUTN      |    |         |                                                      |

| J2  | VDDA_VCO    | Р  | Analog  | LDO output for RFPLL VCO                             |

| К2  | VDDA_CP     | Р  | Analog  | LDO output for RFPLL Charge pump                     |

| L2  | VDDA_PLL    | Р  | Analog  | LDO output for RFPLL Digital                         |

| L1  | TXPA_OUTP   | 0  | RF      | TX Internal Power Amp output                         |

| M1  | TXPA_OUTN   |    |         |                                                      |

| P1  | TXPA_BIAS1  | 0  | Analog  | TX Power Amp Bias1: connect to capacitor             |

| M2  | TXPA_BIAS2  |    |         | TX Power Amp Bias2: connect to capacitor             |

| N3  | TXPA_IN     | I  | RF      | Tx Internal Power Amp input                          |

| N2  | TXPA_V25    | 0  | Analog  | DC power input for Power Amp                         |

| P3  | TXPA_LDOOUT | Р  | Analog  | LDO output for TX PA                                 |

| N1  | VCC_PA2     | Р  | Analog  | Power supply (PA)                                    |

| P2  | VCC_RFTX    | Р  | Analog  | Power supply (PAIO)                                  |

| P4  | TXDA_OUT    | 0  | RF      | TXDA output                                          |

| N4  | VDDA_RFTX   | Р  | Analog  | DC power input for RFTX                              |

| P5  | RFTX_LDOOUT | 0  | Analog  | LDO output for RFTX: connect to VDDA_RFTX            |

| N5  | GPDACOUTP   | 0  | Analog  | GP DAC output                                        |

| N6  | GPDACOUTN   |    |         |                                                      |

| P6  | XIN_32M     | IO | Analog  | X-tal input or TCXO input (32MHz)                    |

| P7  | XOUT_32M    | IO | Analog  | X-tal output (32MHz)                                 |

| P8  | DIG_CPOUT   | 0  | Analog  | Charge pump output for Digital PLL                   |

| N8  | VDD_TCXO    | Р  | Analog  | LDO output for Digital PLL and TCXO buffer           |

| P9  | VCC_IO4     | Р  | Analog  | Power supply (IO4)                                   |

| P10 | VCCD1       | Р  | Analog  | Power supply (Digital)                               |

| N10 | VDDD1       | Р  | Analog  | LDO output for Digital                               |

| N11 | TDO/SWO     | 0  | Digital | JTAG Data Out / optional trace output                |

| N12 | TCK/SWCLK   | I  | Digital | JTAG Clock / Serial Wire Clock                       |

| P11 | TMS/SWDIO   |    | Digital | JTAG Test Mode State / Serial Wire Data Input Output |

| P12 | TDI         |    | Digital | JTAG Data In pin                                     |

| P13 | nTRST       | I  | Digital | JTAG reset pin                                       |

| N14 | PC7         | IO | Digital | Digital IO: Port C                                   |

| M13 | PC6         | IO | Digital | Digital IO: Port C                                   |

| M14 | PC5         | IO | Digital | Digital IO: Port C                                   |

| L13 | PC4         | IO | Digital | Digital IO: Port C                                   |

| No  | Name     | IO | Туре    | Description                             |

|-----|----------|----|---------|-----------------------------------------|

| K14 | PC3      | IO | Digital | Digital IO: Port C                      |

| J13 | PC2      | IO | Digital | Digital IO: Port C                      |

| J14 | PC1      | IO | Digital | Digital IO: Port C                      |

| H13 | PC0      | IO | Digital | Digital IO: Port C                      |

| K13 | RESETb   | I  | Digital | Digital reset pin                       |

| L14 | VCCF     | Р  | Digital | Power supply (F)                        |

| H14 | PB7      | IO | Digital | Digital IO: Port B                      |

| G13 | PB6      | IO | Digital | Digital IO: Port B                      |

| G14 | PB5      | IO | Digital | Digital IO: Port B                      |

| F13 | PB4      | IO | Digital | Digital IO: Port B                      |

| F14 | PB3      | IO | Digital | Digital IO: Port B                      |

| E13 | PB2      | IO | Digital | Digital IO: Port B                      |

| E14 | PB1      | IO | Digital | Digital IO: Port B                      |

| D13 | PB0      | IO | Digital | Digital IO: Port B                      |

| D14 | PA7      | IO | Digital | Digital IO: Port A                      |

| C13 | PA6      | IO | Digital | Digital IO: Port A                      |

| C14 | PA5      | IO | Digital | Digital IO: Port A                      |

| B13 | PA4      | IO | Digital | Digital IO: Port A                      |

| B14 | PA3      | IO | Digital | Digital IO: Port A                      |

| A14 | PA2      | IO | Digital | Digital IO: Port A                      |

| A13 | PA1      | IO | Digital | Digital IO: Port A                      |

| B12 | PA0      | IO | Digital | Digital IO: Port A                      |

| A12 | VCCD2    | Р  | Digital | Power supply (digital)                  |

| A11 | VCCU     | Р  | Digital | Power supply (USB)                      |

| B11 | VDDD2    | Р  | Digital | LDO output for Digital                  |

| B10 | DP       | IO | Digital | USB D+, D-                              |

| A10 | DM       |    |         |                                         |

| A9  | PORb     | I  | Analog  | Power on Reset                          |

|     |          |    |         | Capacitor 1nF should be connected       |

| B9  | PORb_OUT | 0  | Analog  | Power on Reset output (for test)        |

| B8  | WAKEUPb  | I  | Analog  | Wakeup signal                           |

| A8  | VCC_IO3  | Р  | Analog  | Power supply (IO3)                      |

| A7  | XOUT_32K | 0  | Analog  | 32kHz X-tal buffer output               |

| B7  | XIN_32K  | I  | Analog  | 32kHz X-tal buffer output               |

| A6  | GPADC_IN | I  | Analog  | GP ADC input                            |

| B6  | VDDA_DIG | Р  | Analog  | LDO output for ADC and DAC              |

|     | NC       | -  | -       | No connected, these pins should be open |

## 4. Functional Description

#### 4.1 RF

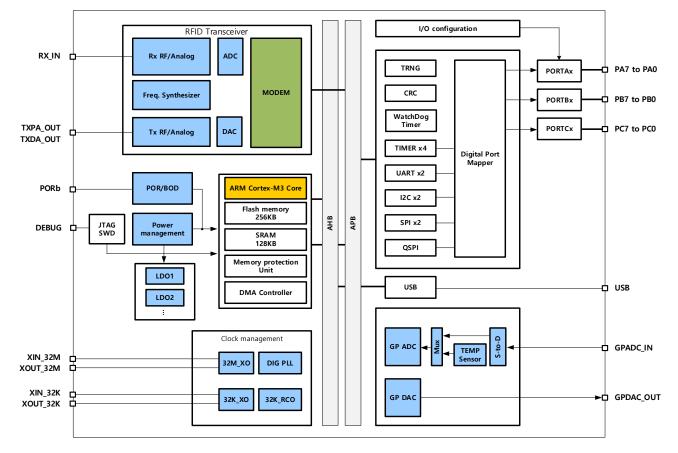

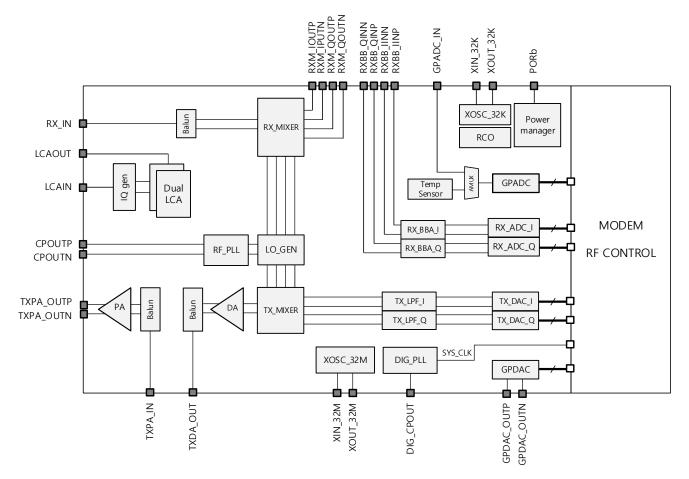

Figure 2 RF block diagram

#### 4.1.1 Receiver path

The receiver consists of a mixer, BBA (Base Band Analog), and ADC. The Rx mixer performs down-conversion of the RF received signal to the Base Band signal. The BBA circuit includes DC offset cancellation, an analog low-pass filter, and a variable gain amplifier. The BBA provides optimized gain, LPF bandwidth, DC cutoff frequency, etc., based on the characteristics of the input signal (magnitude, link frequency, modulation method). The Rx ADC converts the baseband analog signal to a digital signal for the MODEM.

AC coupling or DRM filter is required between the Rx Mixer output (RXM\_IOUTP/N, RXM\_QOUTP/N) and Rx BBA input (RXBB\_IINP/N, RXBB\_QIN). The specifications of the DRM filter are provided through a separate application circuit. The PR7 receiver includes a Leakage Cancellation Amplifier (LCA) to eliminate Tx leakage. An additional 3dB coupler is required, effectively removing leakage even in structures with Tx output power of 30dBm or higher. The Dual LCA particularly adapts dynamically to changes in leakage magnitude due to various antenna S11 (Return loss).

#### 4.1.2 Transmitter path

The PR7 transmitter is composed of a DAC, LPF, mixer, and DA (Driver Amp). The Tx DAC converts the modulated digital baseband signal into an analog signal, and at the Tx mixer, it undergoes up-conversion to a UHF RF signal. To comply with country-specific regulations, appropriate filters (such as SAW filters) may be required at the DA output.

The PR7 includes a built-in Power Amplifier (PA), and the DA output or filter output can be connected to TXPA\_IN for use. The internal PA in PR7 requires a balun for diff-to-single conversion, as it provides a differential output. If a higher output power, such as 30dBm or more, is needed, an external PA is required instead of the internal PA.

#### 4.1.3 Frequency synthesizer

The PR7 has two built-in Frequency synthesizers. The RF\_PLL, utilizing a Fractional-N structure, provides the LO signal for the Rx mixer or Tx mixer. CP\_OUTP and CP\_OUTN serve as the input pins for the differential loop filter of RF\_PLL. DIG\_PLL generates the system clock for the MCU, as well as clocks for the MODEM, ADC, and DAC. The loop filter for DIG\_PLL is connected to DIG\_CPOUT. A 32MHz reference clock is required for the frequency synthesizer. An oscillator buffer for the 32MHz clock is built-in, providing two methods for supplying the reference clock. The first involves connecting a 32MHz TCXO (or 32MHz Oscillator) to XIN\_32M. The second method is connecting a 32MHz Xtal to XIN\_32M and XOUT\_32M.

PR7 includes a low-frequency clock of 32.768KHz for power management and wakeup time control. For more precise time control, an external 32.768kHz Xtal can be connected to XIN\_32K and XOUT\_32K for use.

#### 4.1.4 Others

PR7 features a General Purpose ADC and General Purpose DAC. The GP ADC converts the input at GPADC\_IN into 12-bit digital data. On the other hand, the GP DAC converts 12-bit digital data into an analog signal and outputs it differentially as GPDAC\_OUTP and GPDAC\_PUTN.

#### 4.2 MCU

#### 4.2.1 Feature

- Cortex M3 MCU Core (up to 128MHz)

- 256KB embedded Flash memory with flash cache

- 128KB SRAM

- 2 UART with modem control

- 2 SPI Master/Slave

- 2 I2C Master/Slave

- QSPI Master

- 6 Timer / 2 Dual Timer

- Watchdog Timer

- True Random Number Generator (TRNG)

- GPIO (24bit, pullup, driving strength)

- Configurable Port Muxing

- USB Full Speed Device Controller/PHY

- 12-channel AHB DMA

#### 4.2.2 UART

The UART (Universal Asynchronous Receiver/Transmitter) core provides serial communication capabilities, allowing communication with other computers, modems, or external devices using serial cables and the RS-232 protocol. The UART interface is compatible with the industry-standard National Semiconductors' 16550A device. It offers two UARTs, UART0 and UART1, each equipped with built-in transmit FIFO and receive FIFO. All UARTs support hardware control signals, including CTS and RTS, and can be utilized with DMA controllers.

#### 4.2.3 I2C

I2C is a 2-wire bidirectional serial bus that provides a simple and efficient method for devices to exchange data. It is suitable for applications where intermittent communication over short distances between multiple devices is needed. The I2C standard includes collision detection and arbitration mechanisms to prevent data corruption when multiple masters attempt to control the bus simultaneously. Two I2C interfaces, I2C0 and I2C1, are provided, supporting two transmission speeds: Normal Mode (100Kbps) and Fast Mode (400Kbps).

#### 4.2.4 SPI

SPI (Serial Peripheral Interface) provides both full-duplex and simplex communication modes. It supports both Master and Slave modes and is compatible with the SPI standard of Motorola. Two SPI interfaces, SPI0 and SPI1, are provided, each equipped with built-in transmit FIFO and receive FIFO. Both SPI interfaces can be serviced by the DMA controller.

#### 4.2.5 QSPI (Quad-SPI)

Quad SPI provides a serial communication interface using four data lines, utilizing up to six lines including one Chip Select line and one Clock line. It enables parallel data transmission through the four data lines. Operating solely as a master, Quad SPI can be configured to work in Single (similar to conventional SPI) or Dual modes through the QSPI interface. This interface is commonly used with devices that support Quad SPI communication, such as external flash memory or display devices.

#### 4.2.6 USB

USB supports the USB2.0 Full Speed (12Mbps) interface. It can process the USB protocol and operate as a USB device using the host processor. It has eight endpoints that can be configured via software and supports suspend/resume functionality.

#### 4.2.7 Timer

#### 4.2.7.1 Timer 0~1

This is a 32-bit down-counter timer. It is a basic timer that generates an interrupt when the timer counter reaches 0.

#### 4.2.7.2 Timer 2~5

Timers 2 through 5 support two modes: Input Capture and PWM. Each timer is a 32-bit timer with four independent channels. In Capture mode, the timer counts in the direction set when a pulse with the configured polarity is input to the pin. PWM mode allows for various configurations, including Toggle, Pulse, and PWM modes, by setting the pulse count.

#### 4.2.7.3 Dual Timer

The Dual Timer consists of two programmable 32-bit or 16-bit down counters. The timer can be programmed with either a 32-bit or 16-bit counter and one of the timer modes (free-running, periodic, one-shot).

The dual-input timer generates two interrupts and provides access to a 32-bit free-running counter (FRCs). FRCs operate on a common timer clock and have their clock enable inputs. Each FRC has a prescaler that can divide the activated clock speed by 1, 16, or 256, allowing independent control of the counter speed for each FRC through individual clock activation and prescaler use.

- Free-running mode: The counter wraps around to 0 after reaching the value of 0 and continues counting down from the maximum value.

- Periodic mode: The counter generates interrupts at regular intervals, reloading the original value after surpassing 0.

- One-shot mode: The counter generates an interrupt once and stops until reprogrammed when it reaches 0.

#### 4.2.8 Watchdog timer

The Watchdog Timer is based on a 32-bit down-counter. The Watchdog module generates a regular interrupt based on a programmed value. It monitors the interrupts, and if the counter reaches 0 and stops without the interrupt being cleared, it asserts a reset signal. If the interrupt is not cleared until the counter reaches 0, the watchdog module will re-specify the reset signal. The Watchdog module provides a way to apply a system reset in case of software errors, allowing recovery from software crashes. The watchdog unit can be enabled or disabled as needed.

#### 4.2.9 DMA

DMA (Direct Memory Access) is used to replace CPU functions, such as memory-to-memory, peripheral-tomemory, and memory-to-peripheral transfers. It provides up to 12 DMA channels and can be utilized for controlling peripherals like UART and SPI.

#### 4.2.10 TRNG (True Random Number Generator)

Using TRNG (True Random Number Generator) allows the generation of a random bit stream. TRNG provides full entropy output to the application in 32-bit samples. It is utilized during Frequency Hopping to randomly generate sequences for frequency channels.

#### 4.2.11 Debug Mode

The ARM SWJ-DP interface is integrated to provide a combined JTAG and SWD debug port. The JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and specific sequences on the TMS pin are used to switch between JTAG-DP and SW-DP. Debugging can be controlled through the JTAG/SWD access port using debugging tools.

#### 4.2.12 GPIO

GPIO (General Purpose Input/Output) is a general-purpose I/O interface unit that provides a total of 24 pins. It offers programmable interrupt generation capabilities and supports bit masking using address values. The masked access feature allows reading or writing individual bits or multiple bits in a single transaction. Additionally, it supports pin multiplexing, enabling the switch to alternative functions.

## 4.2.13 Interrupt

| IRQ No | Туре         | IRQ No | Туре           |

|--------|--------------|--------|----------------|

| 0      | Reserved     | 33     | Embedded Flash |

| 2      | Reserved     | 34     | Flash Cache    |

| 5      | RTC          | 44     | TRNG           |

| 6      | All gpio     | 45     | UART0          |

| 8      | Timer0       | 46     | UART1          |

| 9      | Timer1       | 47     | I2C0           |

| 10     | Dual Timer   | 48     | I2C1           |

| 12     | Reserved     | 49     | SPI0           |

| 16     | GPIO A Pin 0 | 50     | SPI1           |

| 17     | GPIO A Pin 1 | 51     | QSPI           |

| 18     | GPIO A Pin 2 | 52     | TIMER2         |

| 19     | GPIO A Pin 3 | 53     | TIMER3         |

| 20     | GPIO A Pin 4 | 54     | TIMER4         |

| 21     | GPIO A Pin 5 | 55     | TIMER5         |

| 22     | GPIO A Pin 6 | 56     | DMA            |

| 23     | GPIO A Pin 7 | 57     | USB            |

| 24     | GPIO B Pin 0 | 60     | GPIO C Pin 0   |

| 25     | GPIO B Pin 1 | 61     | GPIO C Pin 1   |

| 26     | GPIO B Pin 2 | 62     | GPIO C Pin 2   |

| 27     | GPIO B Pin 3 | 63     | GPIO C Pin 3   |

| 28     | GPIO B Pin 4 | 64     | GPIO C Pin 4   |

| 29     | GPIO B Pin 5 | 65     | GPIO C Pin 5   |

| 30     | GPIO B Pin 6 | 66     | GPIO C Pin 6   |

| 31     | GPIO B Pin 7 | 67     | GPIO C Pin 7   |

| 32     | System Error |        |                |

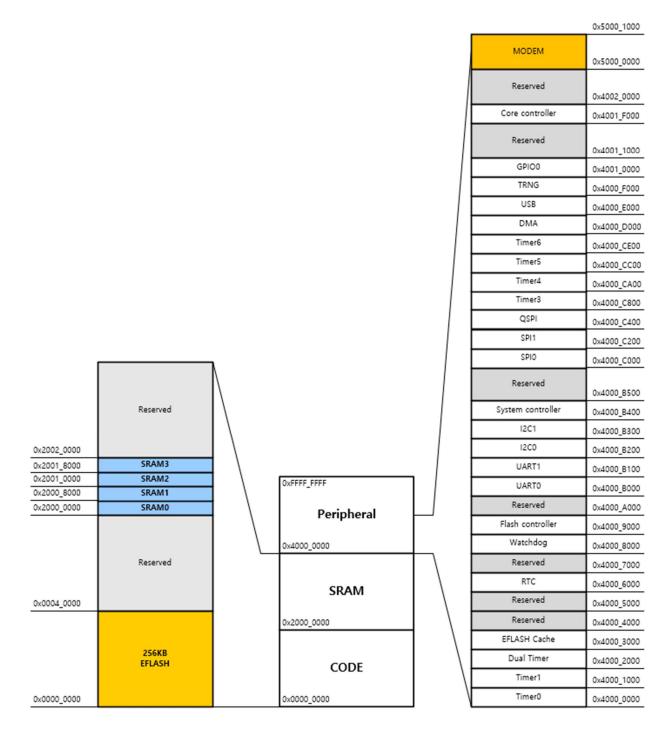

#### 4.2.14 Memory Organization

Figure 3 Memory map

#### 4.2.15 Port Map

The PR7 has 3 x 8bit digital IOs, and each IO supports an alternative function that can be selected from UART, I2C, SPI, QSPI, timer, etc.

#### 4.2.15.1 Port A

| Port   |     | AF1       | AF2      | AF3       | AF4      | AF5      |

|--------|-----|-----------|----------|-----------|----------|----------|

|        | PA0 | UART0_TXD | -        | SPI0_CLK  | QSPI_CLK | TIM2_CH0 |

|        | PA1 | UART0_RXD | -        | SPI0_CS   | QSPI_CS  | TIM2_CH1 |

|        | PA2 | UART0_RTS | I2C0_SCL | SPI0_MISO | QSPI_D0  | TIM2_CH2 |

| Dort A | PA3 | UART0_CTS | I2C0_SDA | SPI0_MOSI | QSPI_D1  | TIM2_CH3 |

| Port A | PA4 | UART1_TXD | -        | SPI1_CLK  | QSPI_D2  | TIM3_CH0 |

|        | PA5 | UART1_RXD | -        | SPI1_CS   | QSPI_D3  | TIM3_CH1 |

|        | PA6 | UART1_RTS | I2C1_SCL | SPI1_MISO | -        | TIM3_CH2 |

|        | PA7 | UART1_CTS | I2C1_SDA | SPI1_MOSI | -        | TIM3_CH3 |

#### 4.2.15.2 Port B

| Port   |     | AF1       | AF2      | AF3       | AF4      | AF5      |

|--------|-----|-----------|----------|-----------|----------|----------|

|        | PB0 | UART0_TXD | -        | SPI0_CLK  | QSPI_CLK | TIM2_CH0 |

|        | PB1 | UART0_RXD | -        | SPI0_CS   | QSPI_CS  | TIM2_CH1 |

|        | PB2 | UART0_RTS | I2C0_SCL | SPI0_MISO | QSPI_D0  | TIM2_CH2 |

| Dort P | PB3 | UART0_CTS | I2C0_SDA | SPI0_MOSI | QSPI_D1  | TIM2_CH3 |

| Port B | PB4 | UART1_TXD | -        | SPI1_CLK  | QSPI_D2  | TIM3_CH0 |

|        | PB5 | UART1_RXD | -        | SPI1_CS   | QSPI_D3  | TIM3_CH1 |

|        | PB6 | UART1_RTS | I2C1_SCL | SPI1_MISO | -        | TIM3_CH2 |

|        | PB7 | UART1_CTS | I2C1_SDA | SPI1_MOSI | -        | TIM3_CH3 |

#### 4.2.15.3 Port C

| Port   |     | AF1       | AF2      | AF3       | AF4      | AF5      |

|--------|-----|-----------|----------|-----------|----------|----------|

|        | PC0 | UART0_TXD | -        | SPI0_CLK  | QSPI_CLK | TIM4_CH0 |

|        | PC1 | UART0_RXD | -        | SPI0_CS   | QSPI_CS  | TIM4_CH1 |

|        | PC2 | UART0_RTS | I2C0_SCL | SPI0_MISO | QSPI_D0  | TIM4_CH2 |

| Dort C | PC3 | UART0_CTS | I2C0_SDA | SPI0_MOSI | QSPI_D1  | TIM4_CH3 |

| Port C | PC4 | UART1_TXD | -        | SPI1_CLK  | QSPI_D2  | TIM5_CH0 |

|        | PC5 | UART1_RXD | -        | SPI1_CS   | QSPI_D3  | TIM5_CH1 |

|        | PC6 | UART1_RTS | I2C1_SCL | SPI1_MISO | -        | TIM5_CH2 |

|        | PC7 | UART1_CTS | I2C1_SDA | SPI1_MOSI | -        | TIM5_CH3 |

## 5. System Control

#### 5.1 Operation mode

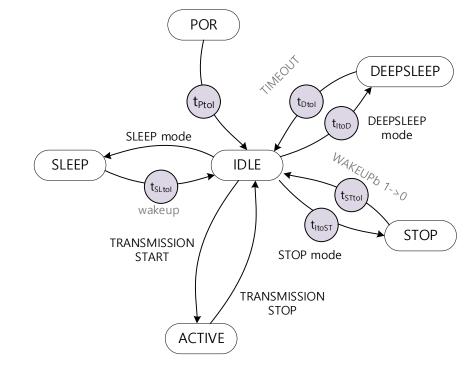

PR7 has five operating modes.

#### 5.1.1 IDLE mode

After the Power On Reset (POR), PR7 enters the IDLE mode. The IDLE mode serves as a preparation stage for transitioning to the ACTIVE mode in response to commands from the HOST. In the ACTIVE mode, tag read/write operations are performed. Once the requested commands are executed, PR7 returns to the IDLE mode.

#### 5.1.2 ACTIVE mode

This is the mode in which PR7 performs tag read/write operations. In fact, all commands related to UHF RFID are executed in this mode. The transition from the IDLE mode to the ACTIVE mode can occur either through commands from the HOST via the serial interface or automatically through firmware automation routines.

#### 5.1.3 SLEEP mode

This is the mode in which the MCU enters a sleep state from the IDLE mode. In the SLEEP mode, various peripherals controlled by the MCU can have their clocks controlled to reduce current consumption. The transition to the IDLE mode is triggered by an external interrupt.

#### 5.1.4 DEEPSLEEP mode

After entering the DEEPSLEEP mode, PR7 will wake up and return to the IDLE mode after a user-defined time has elapsed. During the DEEPSLEEP mode, all blocks except the 32.768kHz low-frequency oscillator and counter are turned off to minimize power consumption. There are two methods for waking up from the DEEPSLEEP mode. The first method involves pulling the WAKEUPb pin low, while the second method entails setting a wakeup timer to wake up the system after a specified time.

#### 5.1.5 STOP mode

In the STOP mode, all blocks of PR7 are turned off, and it can only be awakened by the WAKEUPb pin.

Figure 4 operation mode

The table below shows the transition time for each operation mode

| Parameter                               | Condition                    | Min. | Тур. | Max. | Unit |

|-----------------------------------------|------------------------------|------|------|------|------|

| POR to IDLE time $(t_{Ptol})^{NOTE2}$   | Time from Reset to entering  |      | 160  |      | ms   |

|                                         | IDLE mode                    |      |      |      |      |

| SLEEP to IDLE time $(t_{Stol})$         | Wake up time from SLEEP mode |      | 400  |      | ns   |

|                                         | to IDLE mode                 |      |      |      |      |

| IDLE to DEEPSLEEP time                  | Time from IDLE mode to       |      | 220  |      | us   |

| (t <sub>ltoD</sub> )                    | DEEPSLEEP mode               |      |      |      |      |

| DEEPSLEEP to IDLE time                  | Wakeup time from DEEPSLEEP   |      | 56   |      | ms   |

| (t <sub>Dtol</sub> )                    | mode to IDLE mode            |      |      |      |      |

| IDLE to STOP time (t <sub>ItoST</sub> ) | Time from IDLE mode to STOP  |      | 250  |      | us   |

|                                         | mode                         |      |      |      |      |

| STOP to IDLE time $(t_{STtol})$         | Wakeup time from STOP mode   |      | 55   |      | ms   |

|                                         | to IDLE mode                 |      |      |      |      |

[NOTE1] Refer to the WINE reader control protocol for information on the operating method of the mode control

[NOTE2] This time includes software-related reset processes, such as bootloader checks, RF register initialization, and more. It may vary depending on the firmware configuration of PR7.

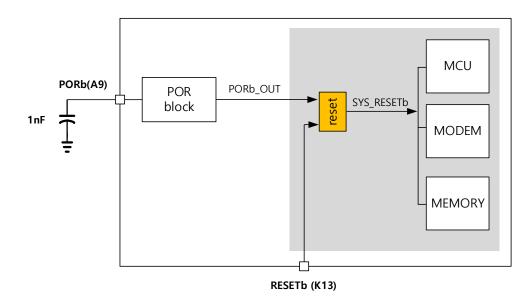

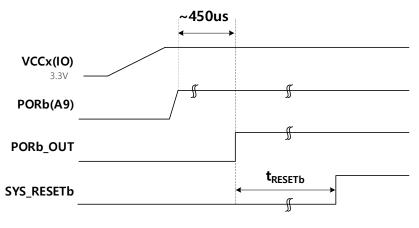

### 6. Power up timing

PR7 has an internal power management circuit. A 1nF capacitor is needed on the PORb pin for the reset timing of the POR block. During power-up, the PORb\_OUT signal generated by the power management block creates the reset signal for the digital parts of PR7 (MCU, MODEM, MEMORY). A manual reset is also possible via RESETb (K13), where RESETb operates as active-low and must remain low for at least 10us.

Figure 5 Reset circuit

The diagram below shows the reset time during power-up. A 40ms hardware reset time is required during power-up.

## 7. Package Information

#### 7.1 Package Dimensions

## 7.2 PCB layout

#### **Disclaimer:**

PHYCHIPS reserves the right to make changes to the information in this document without prior notice. The purchase of PHYCHIPS products does not convey any license under patent rights owned by PHYCHIPS or others. PHYCHIPS does not assume any responsibility for the use of this product. It is the customer's responsibility to make sure that the system complies with regulations.

© PHYCHIPS Inc. All rights reserved.