# **UHF RFID Reader/Writer Module**Specification

# **Contents**

| Revisi | ion History              |    |

|--------|--------------------------|----|

| 1      | Overview                 | 4  |

| 2      | Electrical Specification | 5  |

| 2.1    | Absolute Maximum Ratings | 5  |

| 2.2    | Functional specification | 5  |

| 3      | Pin Description          | 6  |

| 4      | Application Circuit      | 8  |

| 4.1    | Power Supply             | 8  |

| 4.2    | RESETb                   | 8  |

| 4.3    | UART                     | 8  |

| 4.4    | I2C Interface            | 9  |

| 4.5    | GPIO                     | 9  |

| 4.6    | External Interrupt       | 9  |

| 4.7    | ISP Mode                 | 10 |

| 4.8    | Debugger                 | 10 |

| 4.9    | Operation Mode Control   | 11 |

| 4.10   | Available GPIO           | 12 |

| 5      | Channel Number Table     | 13 |

| 5.1    | Narrow US band           | 13 |

| 5.2    | Wide US band             | 14 |

| 5.3    | Korea band               | 15 |

| 5.4    | China band               | 15 |

| 5.5    | EU band                  | 16 |

| 6      | Dimension                | 17 |

| 7      | Footprint                | 18 |

| 8      | Packing Information      | 20 |

| 8.1    | Tray dimension           | 20 |

| 8.2    | Outer box dimension      | 20 |

| 9      | Reflow information       | 21 |

| 10     | Address Information      | 22 |

# **Revision History**

| Version | Date       | Page                     | Description                                                                                                                |

|---------|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1.0.0   | 2014.12.15 |                          | Preliminary                                                                                                                |

| 1.1.0   | 2015.05.11 |                          | Modified pin diagram                                                                                                       |

| 1.1.1   | 2015.05.14 |                          | Added available GPIO and footprint information                                                                             |

| 1.1.2   | 2015.06.02 |                          | Changed name Modified pin description: VCCIN and VCC36P Modified application note Removed description about deepsleep mode |

| 1.1.3   | 2015.07.07 |                          | Modified Frequency range and table                                                                                         |

| 1.1.4   | 2015.07.28 |                          | Added reflow chart Added information to 2. Electrical specification                                                        |

| 1.1.5   | 2015.07.30 |                          | Typo error fixed                                                                                                           |

| 1.1.6   | 2015.08.10 |                          | Fixed dimension and footprint                                                                                              |

| 1.1.7   | 2017.01.12 | 4<br>17<br>20            | Modified the block diagram  Modified the label part of module, figure 8  Modified the dimension of inner form & outer box  |

| 2.0.0   | 2017.11.29 | 5,6,7,<br>8,12,<br>17,20 | Changed DTC control method from I2C to SPI Fixed typo error of dimension Changed the packing method                        |

| 2.0.1   | 2019.06.14 |                          | Changed the name of channel table                                                                                          |

| 2.0.2   | 2019.10.17 | 11                       | Fixed typo error in section 4.9 Operation Mode Control                                                                     |

| 2.0.3   | 2019.11.25 |                          | Fixed pin description table : SWDIO&SWCLK                                                                                  |

#### 1 Overview

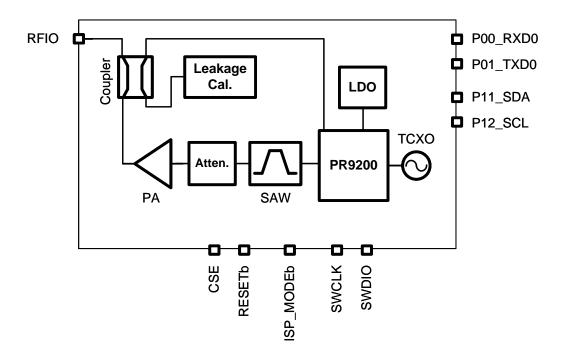

The RED5 is a UHF RFID Reader hybrid module which integrates high performance UHF RFID reader chipset, TCXO, Balun, Coupler, Saw filter, Power amp and low pass filter.

UHF RFID reader chipset uses PR9200 of PHYCHIPS which integrates 900MHz radio, baseband processor, industry standard enhanced Cortex-M0 MCU, memory (64k Flash & 16k SRAM) and many other features. This module fully compliant with ISO18000-6C/EPC Global Gen II reader protocol and provide all functions of PR9200. Also reduce size, cost and power consumption. The RED5 includes automatic tx leakage cancellation to improve reader's performance and compensate sensitivity for some variation according to the surrounding environment. Also it helps a developer adopt the proper antenna and realize the optimized RFID reader system more easily and quickly.

Figure 1 Block Diagram

# 2 Electrical Specification

# 2.1 Absolute Maximum Ratings

| No.  | Item                    | Unit Test Condition |                | Specification |      |     | Remark |

|------|-------------------------|---------------------|----------------|---------------|------|-----|--------|

| 140. | item                    | Oilit               | rest condition | min           | Тур. | max | Kemark |

| 1    | Supply voltage : VCCIN  | V                   | -              | 1             | ı    | 6.0 |        |

| 2    | Supply voltage : VCC36P | V                   | -              | -             | -    | 4.5 |        |

| 3    | Storage temperature     | °C                  | -              | -40           |      | 85  |        |

## 2.2 Functional specification

| No. | Item               |                     | Unit                   | Test Condition    | Specification        |      |     | Remark |

|-----|--------------------|---------------------|------------------------|-------------------|----------------------|------|-----|--------|

| NO. | ite                | '''                 | Offit   Test Condition |                   | min                  | Тур. | max | Remark |

| 1   | Frequency Rang     | je <sup>NOTE1</sup> | MHz                    |                   | 860                  |      | 960 |        |

| 2   | Tx Power           |                     | dBm                    |                   | 0                    |      | 30  |        |

| 3   | Dynamic Range      |                     | dB                     |                   |                      | 30   |     |        |

| 3   | Spurious NOTE2     |                     | dBm                    |                   | Korea (Ko<br>US (FCC | •    |     |        |

| 4   | Impedance          |                     | Ω                      |                   |                      | 50   |     | RF I/O |

| 5   | DC Power           | VCCIN               | V                      |                   | 3.5                  |      | 5   |        |

| 5   | DC Power           | VCC36P              | V                      |                   |                      | 3.6  | 4.2 |        |

| 6   | Digital interface  | IO voltage          | V                      |                   |                      | 3.3  |     |        |

| 7   | Operating Temp     | erature             | °C                     |                   | -20                  |      | 70  |        |

| 8   | Operating Humidity |                     | %                      |                   | 0                    |      | 90  |        |

|     |                    | Power Down          | uA                     | Active current is |                      |      | 20  |        |

| 9   | 9 Current Idle     |                     | mA                     | measured at 30dBm |                      |      | 20  |        |

|     |                    | Active              | Α                      | output CW.        |                      | 1.37 |     |        |

NOTE1. If you want to know the supportable channel and frequency, refer to 5. Channel number table.

NOTE2. Other regulation such as SRRC will be updated soon.

#### Firmware Default Function

| No. | Item                     | Status               | Remark |

|-----|--------------------------|----------------------|--------|

| 1   | Firmware Version         | RED5_v3.x.x or later |        |

| 2   | Region                   | -                    |        |

| 3   | Frequency Hopping        | ON                   |        |

| 4   | Q                        | Dynamic Q            |        |

| 5   | Modulation Type          | DSB-ASK              |        |

| 6   | Back Link Frequency(BLF) | 250 kHz              |        |

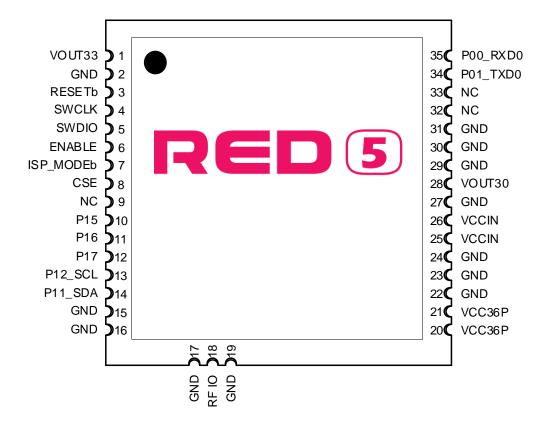

# 3 Pin Description

**Figure 2 Pin Description**

| No. | Pin Name  | Description                                                                                                                      |  |  |  |  |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | VOUT33    | Internal LDO 3.3V output for PR9200 SOC                                                                                          |  |  |  |  |

| 2   | GND       | Ground                                                                                                                           |  |  |  |  |

| 3   | RESETb    | Reader SOC Reset signal 0: reset                                                                                                 |  |  |  |  |

| 4   | SWCLK     | Serial Wire Debug Clock                                                                                                          |  |  |  |  |

| 5   | SWDIO     | Serial Wire Debug data in out                                                                                                    |  |  |  |  |

| 6   | ENABLE    | Enable pin for RED5. It turns on/off internal LDOs                                                                               |  |  |  |  |

| 0   | LNABLE    | Logic high : enable, Logic low : disable (POWER DOWN)                                                                            |  |  |  |  |

|     |           | When ISP_MODEb is Logic 'Low', ISP mode is set as shown below table                                                              |  |  |  |  |

|     |           | Pin No. 7 12 11 10                                                                                                               |  |  |  |  |

|     |           | Pin Name ISP_MODEb P17 P16 P15                                                                                                   |  |  |  |  |

| 7   | ISP_MODEb | Normal 1 GPIO/INT GPIO/INT GPIO/INT                                                                                              |  |  |  |  |

|     |           | FLASH UART ISP 0 0 0 0                                                                                                           |  |  |  |  |

|     |           | [CAUTION] Except ISP mode, ISP_MODEb should be set logic 'High' for                                                              |  |  |  |  |

|     |           | robust stability for FLASH memory                                                                                                |  |  |  |  |

| 8   | CSE       | Chip Select Enable. Internally connected to VCC33.                                                                               |  |  |  |  |

| 0   |           | For the power control of RED5, use ENABLE pin                                                                                    |  |  |  |  |

| 9   | NC        | Not Connection                                                                                                                   |  |  |  |  |

| 10  | P15       | User configurable general purpose I/O port                                                                                       |  |  |  |  |

| 11  | P16       | User configurable general purpose I/O port or External Interrupt 4                                                               |  |  |  |  |

| 12  | P17       | User configurable general purpose I/O port or External Interrupt 5                                                               |  |  |  |  |

| 13  | P12_SCL   | User configurable general purpose I/O port or I2C Clock The pull-up resistor is always switched on. Reserved Address: 0x70, 0x71 |  |  |  |  |

|     |           | User configurable general purpose I/O port or I2C Data In / Out                                                                  |  |  |  |  |

| 14  | P11_SDA   | The pull-up resistor is always switched on.                                                                                      |  |  |  |  |

|     |           | Reserved Address : 0x70, 0x71                                                                                                    |  |  |  |  |

| 15  | GND       | Ground                                                                                                                           |  |  |  |  |

| 16  | GND       | Ground                                                                                                                           |  |  |  |  |

| 17  | GND       | Ground                                                                                                                           |  |  |  |  |

| 18  | RF IO     | RF input/output. Antenna port                                                                                                    |  |  |  |  |

| 19  | GND       | Ground                                                                                                                           |  |  |  |  |

| 20  | VCC36P    | DC power input for Power Amp                                                                                                     |  |  |  |  |

| 21  | VCC36P    | DC power input for Power Amp                                                                                                     |  |  |  |  |

| 22  | GND       | Ground                                                                                                                           |  |  |  |  |

| 23  | GND       | Ground                                                                                                                           |  |  |  |  |

| 24  | GND       | Ground                                                                                                                           |  |  |  |  |

| 25  | VCCIN     | DC power input for module except PA                                                                                              |  |  |  |  |

| 26  | VCCIN     | DC power input for module except PA                                                                                              |  |  |  |  |

| 27  | GND       | Ground                                                                                                                           |  |  |  |  |

| 28  | VOUT30    | Internal LDO output for PA BIAS                                                                                                  |  |  |  |  |

| 29  | GND       | Ground                                                                                                                           |  |  |  |  |

| 30  | GND       | Ground                                                                                                                           |  |  |  |  |

| 31  | GND       | Ground                                                                                                                           |  |  |  |  |

| 32  | NC        | Not Connection                                                                                                                   |  |  |  |  |

| 33  | NC        | Not Connection                                                                                                                   |  |  |  |  |

| 34  | P01_TXD0  | User configurable general purpose I/O port or UART0 Output                                                                       |  |  |  |  |

| 35  | P00_RXD0  | User configurable general purpose I/O port or UART0 Input                                                                        |  |  |  |  |

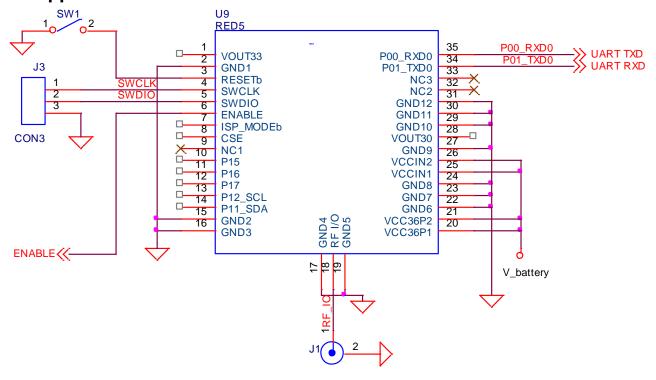

## 4 Application Circuit

Figure 3 Application Circuit

#### 4.1 Power Supply

DC power for RED5 is VCCIN (pin25,26) and VCC36P (pin20,21). There are 2 LDO inside module. One is to supply for PR9200 which DC voltage is 3.3 volts (typ.). The other is to supply for VBIAS for power amp which is 3.0V. VCCIN is connected to input of LDOs. But, VCC36P is connected to PA without internal LDO. Total current consumption of RED5 is typically 1.37A at 30dBm Tx CW output power.

#### 4.2 RESETb

RED5 provides RESET for controlling PR9200, which can control by RESETb (Pin 3). In order to properly operate RESET function, RESETb pin should be connected to ground during at least 2us. [NOTE] RED5 have internal RESET circuit including POR (Power On Reset) and BOD (Brown Output Detector).

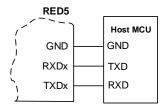

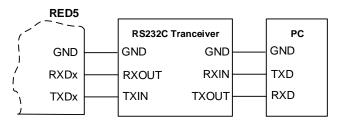

#### **4.3 UART**

The serial interface is assigned with two wires. RXD0, which pin is assigned to pin 35, is for receiving command from host and TXD0, which pin is assigned to pin 34, is for transmitting response to host. Pin connection is shown as below figure.

Figure 4 Host MCU Connection

RS232C transceiver is required to interface with PC that connection diagram is shown as below figure.

Figure 5 RS232 transceiver connection

Following configuration is used for interfacing to USB transceiver.

Figure 6 USB transceiver connection

#### 4.4 I2C Interface

The I2C bus uses 2-wires (SDA and SCL) to transfer information between devices connected to the bus.

- Only two bus wires are required; a serial data line (SDA) and a serial clock line (SCL)

- The completely integrated I2C-bus protocol eliminates the need for address decoders and other glue logic.

- Each device connected to the bus is software addressable by a unique address and simple master/slave relationships exist at all times; master can operate as master-transmitter or as masterreceiver.

- It's a true multi-master bus including collision detection and arbitration to prevent data corruption if two

or more masters simultaneously initiate data transfer.

- Serial, 8-bit oriented, bi-directional data transfers can be made at up to 100kbit/s in the Standard-mode, up to 300kbit/s in the Fast-mode.

- The number of Ics that can be connected to the same bus is limited only by a maximum bus capacitance of 400pF.

#### 4.5 **GPIO**

RED5 provides 7 bi-directional I/O ports including I2C while default serial interface is UART.

#### 4.6 External Interrupt

RED5 provides 3 external interrupt that is unstoppable except by reset.

- · Dedicated non-maskable Interrupt input.

- Support for both level-sensitive and pulse-sensitive interrupt lines.

#### 4.7 ISP Mode

In order to enter UART ISP mode, some hardware setting is required. Set pins ISP\_MODEb, P17, P16 and P15 to logic "Low".

| Mode name | F         | I/W cont | rol |     | Programming Port |

|-----------|-----------|----------|-----|-----|------------------|

| Wode name | ISP_MODEb | P17      | P16 | P15 | Frogramming Fort |

| ISP UART  | 0         | 0        | 0   | 0   | UART0            |

If your module has normally operated firmware, you can update firmware without hardware setting. It is IAP mode. Please refer to RED\_FDM.pdf

### 4.8 **Debugger**

In order to debug firmware, these ports should be connected with H/W debugger which is available on both the ULINK2 and Co-LINK. (for details, please refer to the 'RED\_FDM.pdf')

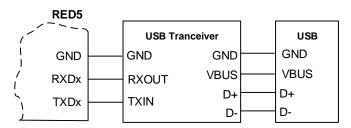

#### 4.9 Operation Mode Control

RED5 is configured in 5 main modes of operation according to PR9200.

The following table describes block condition and current according to each operation state.

Operation state

| Ctata nama    | LI/M/ oot | PR     | R9200   | PA  | ourront                | Function                                                    |

|---------------|-----------|--------|---------|-----|------------------------|-------------------------------------------------------------|

| State name    | H/W set   | Analog | Digital | PA  | current                | runction                                                    |

| POWER<br>DOWN | ENABLE=0  | OFF    | OFF     | OFF | 20uA                   | Module power off                                            |

| SLEEP         | ENABLE=1  | OFF    | Sleep   | OFF | 15mA                   | Sleep mode,<br>Wake-up<br>internal/external<br>interrupt.   |

| IDLE          | ENABLE=1  | OFF    | ON      | OFF | 20mA                   | Block initialization                                        |

| ACTIVE        | ENABLE=1  | ON     | ON      | ON  | 1.37A <sup>NOTE1</sup> | Ramp-up<br>Tag read / write /<br>access / lock<br>Ramp-down |

NOTE1. Active current is measured at Tx CW condition.

The state diagram shows the modes RED5 can operate in. it also include transition time between the states. When RED5 enter ACTIVE mode, RF Block is activated and ramp-up the system and it start to read RFID tag. Entering IDLE mode from POWER DOWN mode, initial time is needed. The initial time of RED5 is 21ms including system power ON.

Figure 7 Operation Sequence

#### 4.10 Available GPIO

RED5 is based on PR9200 SOC. In order to configure the functions of module, some GPIO of PR9200 are already used. Below table shows the available GPIO which is marked in yellow box.

| GPIO | GPIO Function    | RED5                            |

|------|------------------|---------------------------------|

| P00  | UART0 RXD        | UART_RXD0                       |

| P01  | UART0 TXD        | UART_TXD0                       |

| P02  | Ext.0            | Internally used (Ext PA_EN)     |

| P03  | Ext.1            | Internally used                 |

| P04  | SSP TXDS         | Internally used                 |

| P05  | SSP RXDS         | Internally used                 |

| P06  | SSP SCK          | Internally used                 |

| P07  | SSP SEL          | Reserved                        |

| P10  | Ext.2            | Internally used                 |

| P11  | I2C SDA          | Internally used NOTE1           |

| P12  | I2C SCL          | Internally used NOTE1           |

| P13  | UART1 RXD(Ext.3) | Internally used                 |

| P14  | UART1 TXD        | Internally used                 |

| P15  | -                |                                 |

| P16  | Ext.4            | IRQ (SPI, I2C) <sup>NOTE2</sup> |

| P17  | Ext.5            |                                 |

NOTE1. Current Slave address 0x70, 0x71 are used. Other Slave address are available NOTE2. When you use I2C Interface, P16 is required. If not, you can use this pin

# **5 Channel Number Table**

#### 5.1 Narrow US band

| Channel | Channel Frequency | Channel | Channel Frequency |

|---------|-------------------|---------|-------------------|

| 1       | 917.10 MHz        | 26      | 922.10 MHz        |

| 2       | 917.30 MHz        | 27      | 922.30 MHz        |

| 3       | 917.50 MHz        | 28      | 922.50 MHz        |

| 4       | 917.70 MHz        | 29      | 922.70 MHz        |

| 5       | 917.90 MHz        | 30      | 922.90 MHz        |

| 6       | 918.10 MHz        | 31      | 923.10 MHz        |

| 7       | 918.30 MHz        | 32      | 923.30 MHz        |

| 8       | 918.50 MHz        | 33      | 923.50 MHz        |

| 9       | 918.70 MHz        | 34      | 923.70 MHz        |

| 10      | 918.90 MHz        | 35      | 923.90 MHz        |

| 11      | 919.10 MHz        | 36      | 924.10 MHz        |

| 12      | 919.30 MHz        | 37      | 924.30 MHz        |

| 13      | 919.50 MHz        | 38      | 924.50 MHz        |

| 14      | 919.70 MHz        | 39      | 924.70 MHz        |

| 15      | 919.90 MHz        | 40      | 924.90 MHz        |

| 16      | 920.10 MHz        | 41      | 925.10 MHz        |

| 17      | 920.30 MHz        | 42      | 925.30 MHz        |

| 18      | 920.50 MHz        | 43      | 925.50 MHz        |

| 19      | 920.70 MHz        | 44      | 925.70 MHz        |

| 20      | 920.90 MHz        | 45      | 925.90 MHz        |

| 21      | 921.10 MHz        | 46      | 926.10 MHz        |

| 22      | 921.30 MHz        | 47      | 926.30 MHz        |

| 23      | 921.50 MHz        | 48      | 926.50 MHz        |

| 24      | 921.70 MHz        | 49      | 926.70 MHz        |

| 25      | 921.90 MHz        | 50      | 926.90 MHz        |

NOTE1. The available band in US is from 902MHz to 928MHz. but in many application, antennas can't cover this all range. So RED series support narrow US band. It also meet FCC regulation.

If you want, you can use all US band named Wide US (North America previously) band as table 5.2

# 5.2 Wide US band

| Channel | Channel Frequency | Channel | Channel Frequency |

|---------|-------------------|---------|-------------------|

| 1       | 902.75 MHz        | 26      | 915.25 MHz        |

| 2       | 903.25 MHz        | 27      | 915.75 MHz        |

| 3       | 903.75 MHz        | 28      | 916.25 MHz        |

| 4       | 904.25 MHz        | 29      | 916.75 MHz        |

| 5       | 904.75 MHz        | 30      | 917.25 MHz        |

| 6       | 905.25 MHz        | 31      | 917.75 MHz        |

| 7       | 905.75 MHz        | 32      | 918.25 MHz        |

| 8       | 906.25 MHz        | 33      | 918.75 MHz        |

| 9       | 906.75 MHz        | 34      | 919.25 MHz        |

| 10      | 907.25 MHz        | 35      | 919.75 MHz        |

| 11      | 907.75 MHz        | 36      | 920.25 MHz        |

| 12      | 908.25 MHz        | 37      | 920.75 MHz        |

| 13      | 908.75 MHz        | 38      | 921.25 MHz        |

| 14      | 909.25 MHz        | 39      | 921.75 MHz        |

| 15      | 909.75 MHz        | 40      | 922.25 MHz        |

| 16      | 910.25 MHz        | 41      | 922.75 MHz        |

| 17      | 910.75 MHz        | 42      | 923.25 MHz        |

| 18      | 911.25 MHz        | 43      | 923.75 MHz        |

| 19      | 911.75 MHz        | 44      | 924.25 MHz        |

| 20      | 912.25 MHz        | 45      | 924.75 MHz        |

| 21      | 912.75 MHz        | 46      | 925.25 MHz        |

| 22      | 913.25 MHz        | 47      | 925.75 MHz        |

| 23      | 913.75 MHz        | 48      | 926.25 MHz        |

| 24      | 914.25 MHz        | 49      | 926.75 MHz        |

| 25      | 914.75 MHz        | 50      | 927.25 MHz        |

#### 5.3 Korea band

| Channel | Channel Frequency | Channel | Channel Frequency |

|---------|-------------------|---------|-------------------|

| 1       | 917.1 MHz         | 17      | 920.30 MHz        |

| 2       | 917.30 MHz        | 18      | 920.50 MHz        |

| 3       | 917.50 MHz        | 19      | 920.70 MHz        |

| 4       | 917.70 MHz        | 20      | 920.90 MHz        |

| 5       | 917.90 MHz        | 21      | 921.10 MHz        |

| 6       | 918.10 MHz        | 22      | 921.30 MHz        |

| 7       | 918.30 MHz        | 23      | 921.50 MHz        |

| 8       | 918.50 MHz        | 24      | 921.70 MHz        |

| 9       | 918.70 MHz        | 25      | 921.90 MHz        |

| 10      | 918.90 MHz        | 26      | 922.10 MHz        |

| 11      | 919.10 MHz        | 27      | 922.30 MHz        |

| 12      | 919.30 MHz        | 28      | 922.50 MHz        |

| 13      | 919.50 MHz        | 29      | 922.70 MHz        |

| 14      | 919.70 MHz        | 30      | 922.90 MHz        |

| 15      | 919.90 MHz        | 31      | 923.10 MHz        |

| 16      | 920.10 MHz        | 32      | 923.30 MHz        |

NOTE1. The channels written in Bold can be used by 4W (CH 2,5,8,11,14,17) The channels (CH1,3,4,6,7,9,10,12,13,15,16,18,19) are used by 3mW

#### 5.4 China band

| Channel | Channel Frequency | Channel | Channel Frequency |

|---------|-------------------|---------|-------------------|

| 1       | 920.125 MHz       | 11      | 922.625 MHz       |

| 2       | 920.375 MHz       | 12      | 922.875 MHz       |

| 3       | 920.625 MHz       | 13      | 923.125 MHz       |

| 4       | 920.875 MHz       | 14      | 923.375 MHz       |

| 5       | 921.125 MHz       | 15      | 923.625 MHz       |

| 6       | 921.375 MHz       | 16      | 923.875 MHz       |

| 7       | 921.625 MHz       | 17      | 924.125 MHz       |

| 8       | 921.875 MHz       | 18      | 924.375 MHz       |

| 9       | 922.125 MHz       | 19      | 924.625 MHz       |

| 10      | 922.375 MHz       | 20      | 924.875 MHz       |

## 5.5 **EU band**

| Channel | Channel Frequency |

|---------|-------------------|

| 1       | -                 |

| 2       | -                 |

| 3       | -                 |

| 4       | 865.70 MHz        |

| 5       | -                 |

| 6       | -                 |

| 7       | 866.30 MHz        |

| 8       | -                 |

| 9       | -                 |

| 10      | 866.90 MHz        |

| 11      | -                 |

| 12      | -                 |

| 13      | 867.50 MHz        |

| 14      | -                 |

| 15      | -                 |

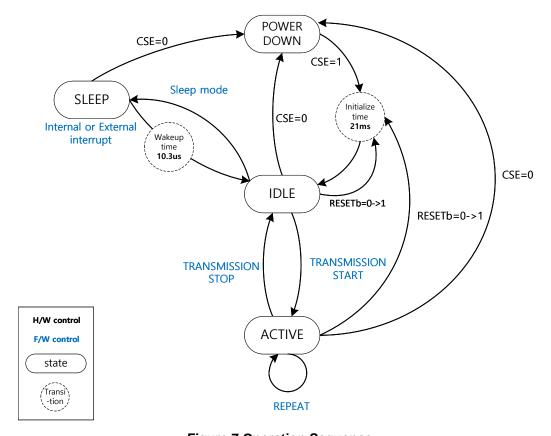

# 6 Dimension

Figure 8 Dimension

| Package on Dimension (Unit : mm) |      |       |      |        |

|----------------------------------|------|-------|------|--------|

| SYM                              | MIN  | TYP   | MAX  | Remark |

| Α                                | 23.5 | 24    | 24.5 |        |

| В                                | 2.9  | 3     | 3.3  |        |

| С                                |      | 2.475 |      |        |

| D                                |      | 6.145 |      |        |

| E                                |      | 6.55  |      |        |

| F                                |      | 8.37  |      |        |

| а                                |      | 1.5   |      |        |

| b                                |      | 0.75  |      |        |

| С                                |      | 1.27  |      |        |

| d                                |      | 3.3   |      |        |

| е                                |      | 3.3   |      |        |

# 7 Footprint

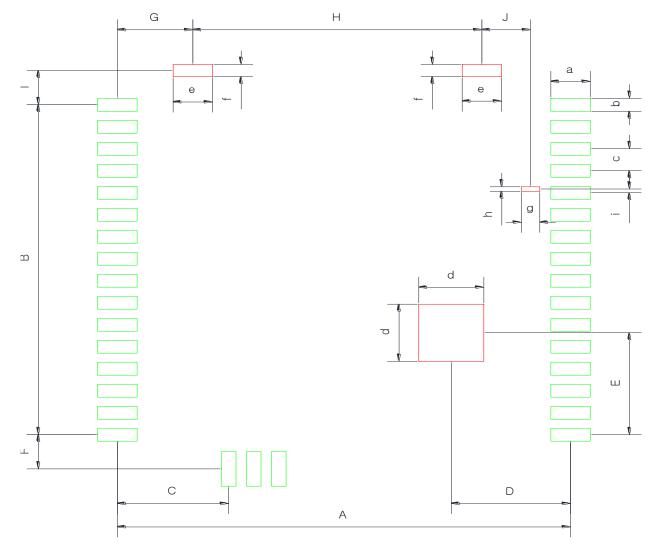

Figure 9 Footprint

| Footprint on Dimension (Unit : mm) |     |       |     |        |

|------------------------------------|-----|-------|-----|--------|

| SYM                                | MIN | TYP   | MAX | Remark |

| A                                  |     | 23.00 |     |        |

| В                                  |     | 19.05 |     |        |

| С                                  |     | 5.65  |     |        |

| D                                  |     | 6.05  |     |        |

| E                                  |     | 5.89  |     |        |

| F                                  |     | 1.98  |     |        |

| G                                  |     | 3.83  |     |        |

| Н                                  | `   | 14.67 |     |        |

| I                                  |     | 1.98  |     |        |

| J                                  | `   | 2.48  |     |        |

| Footprint on Dimension (Unit : mm) |     |      |     |        |

|------------------------------------|-----|------|-----|--------|

| SYM                                | MIN | TYP  | MAX | Remark |

| а                                  |     | 2.10 |     |        |

| b                                  |     | 0.80 |     |        |

| С                                  |     | 1.27 |     |        |

| d                                  |     | 3.30 |     |        |

| е                                  |     | 2.00 |     |        |

| f                                  |     | 0.70 |     |        |

| g                                  |     | 0.93 |     |        |

| h                                  |     | 0.26 |     |        |

| i                                  |     | 0.22 |     |        |

NOTE1. Red box of Figure 9 can be connected to GND.

NOTE2. the area 'd x  $\ddot{d}$ ' and 'g x h' are heat sink. The area 'dxd' is for PA.

#### 8 Packing Information

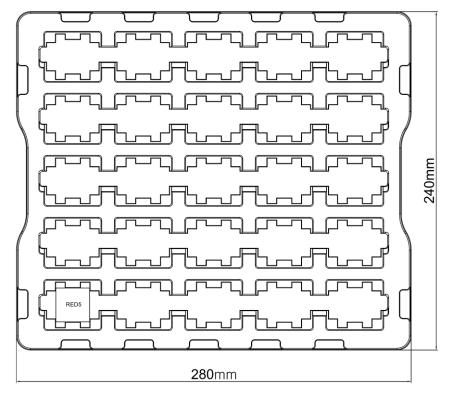

Packing materials for the RED5 shipment consist of the anti-static tray and the outer box which can hold up to five hundred pieces of the RED5 each box.

#### 8.1 Tray dimension

Dimension of the tray to store the RED5, which can hold up to 25 pcs of the RED5, is approximately measured to W = 280mm, L = 240mm, H = 10mm. Tray helps to avoid both interference between the products and static from the outside. Detailed shape refer to figure 10 as below.

Figure 10 Dimension of the tray

#### 8.2 Outer box dimension

The outer box is made printed card board, which may avoid dust, moisture and shock from the outside and convenient to ship. Dimension of the outer box is approximately measured to W = 285mm, L = 250mm, H = 115mm.

X Packing materials are able to change dimension larger or smaller according to shipped quantity of mass product or/and internal policies so that shipment can be controlled easily and safely.

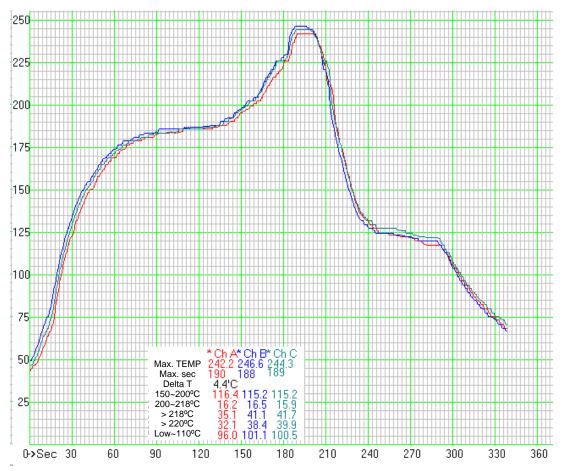

## 9 Reflow information

The recommended reflow profile is shown in figure 11.

Figure 11 Reflow chart

#### 10 Address Information

PHYCHIPS Inc.

#104, 187 Techno-2ro, Yuseong-gu, Daejeon, Korea(Yongsan-dong, Migun Technoworld 2), 34025 http://www.phychips.com

sales@phychips.com Tel: +82-42-864-2402 Fax: +82-42-864-2403

**Disclaimer:** PHYCHIPS reserves the right to make changes to the information in this document without prior notice. The purchase of PHYCHIPS products does not convey any license under patent rights owned by PHYCHIPS or others. PHYCHIPS does not assume any responsibility for the use of this product. It is the customer's responsibility to make sure that the system complies with regulations.

© 2019 PHYCHIPS Inc. All rights reserved. The reproduction of this document is NOT allowed without approval of PHYCHIPS Inc.